近年来,人工智能正在从互联网行业向通信、制造、能源、医疗、政府等各行各业渗透,成为了社会经济活动中最具变革的力量。得益于5G技术的发展,AI在向这些传统行业落地应用的过程中,延伸到了网络的边缘端:通信运营商开始部署MEC,基于基站中的边缘计算设施为附近设备产生的数据提供AI分析,钢铁厂可基于边缘计算平台的支持,实现产品智能质检模型下发和数据回传等等,我们可以看到越来越多的AI场景在边缘端落地应用。

据IDC预测,到2023年将有超过50%的新建企业基础设施被部署在边缘,而目前这一比例不到10%。AI走到边缘,意味着什么?

IT标准与CT标准的碰撞

AI走到边缘最直接的挑战是物理环境的变化。AI服务器对云数据中心的空间、散热等等都有严格的规定,可随着AI场景离人们越来越近,边缘端受限的物理空间、复杂的环境都在阻碍着AI向边缘的广泛落地。

在这些不同环境的背后,其实是云端数据中心IT(Information Technology)标准与边缘端CT(Communication Technology )标准有着本质的区别。

IT基础设施是规模化的,比如阿里巴巴等互联网数据中心,承载其电商业务的服务器有几十万台,面向单一业务呈现出大规模、集中化的趋势。但是CT的数据中心,也就是传统的电信数据中心不是规模化的,因为运营商不太需要把流量汇聚到一起,而是要快速得下发下去,到了5G,更是如此,所以CT的规模化效应是远低于IT的。但电信数据中心的多样化远高于IT,因为电信运营商网络要全覆盖,不同的环境都要适应,比如青藏高原就很少能有互联网数据中心,可电信数据中心就不能少,可以看出CT面临的是多元化的需求。

追其根本,是因为IT是以计算为核心,CT是以网络流量为核心的。IT数据中心以服务器等计算设施为核心,需要更强的计算性能,更大的体积,设备一般深度80厘米以上,可达120厘米,也因为IT设备规模化、集中化,所以环境需求单一。而CT以流量为核心,内部扩展要求低,所以设备更加小巧,深度一般在40厘米左右,可靠性、适应性的要求高。

客户需求对行业规范的挑战

边缘计算是IT和CT的融合,要在CT的规范中,履行IT功能。两个行业标准的融合往往是痛苦的,对于执行主体——厂商来说,尤其如此。

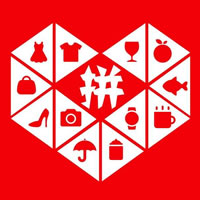

浪潮就接到过某个通信大厂边缘AI算力的定制化需求。客户提出要开发一款可以部署在边缘端的最强AI算力服务器,让边缘数据中心具备最强的AI训练及推理能力。该服务器需部署于600mm深的电信机柜内,因此服务器设备体积和内部部件的规划为19英寸宽,10.5英寸(6U)高,46厘米深,支持2个CPU芯片和32颗AI芯片。

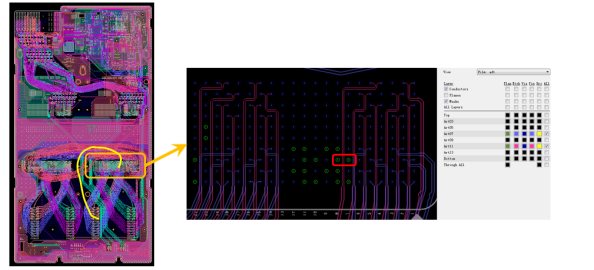

浪潮AI边缘服务器前视图

AI芯片是以模组方式而不是传统的芯片方式供货给设备商,而该模组主要应用于IT场景,其140*78mm的尺寸是按照IT的大机柜场景设计的,在CT标准的狭小机箱内实现32颗AI芯片是极具挑战的。浪潮计划采用8个1U宽,5U高的LC槽位,每槽位4颗AI芯片互连实现32颗AI芯片的规格。

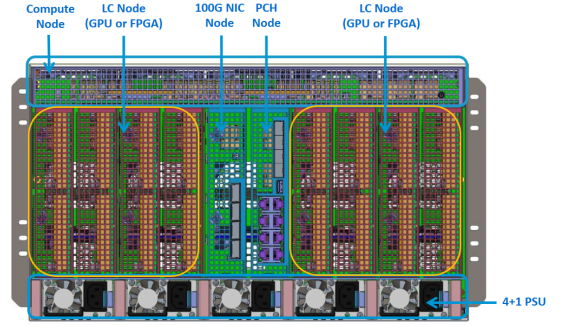

受物理空间限制,一块LC板上只能放置2个AI芯片模组,如何在这样的槽位内实现4个AI模组是达成该产品规格的关键问题。针对该问题,浪潮提出桥接,对扣,Retimer三种解决方案。由于芯片放置于AI模组上,模组同PCB连接时本身需要一对连接器,无论哪种方案都会涉及到AI芯片的25Gbps多次跨越连接器的问题。依据芯片厂家规范,4颗芯片无法多次跨越连接器,也就无法分布在两块单板上。但客户需求是最强的AI算力,若不能实现单槽位4个 AI芯片互联,服务器计算能力也会下降,无法满足客户需求。那就只剩一个选择,突破厂家规范,解决25Gbps多次跨连接器的信号完整性问题,实现4颗芯片分布在2个板上互连。

三种芯片连接方案

跨板互连方案最大的技术挑战是信号完整性设计。因为跨板互连方案不仅会导致信号传输距离大幅增加,而且当25Gbps信号多次跨越连接器,会加大25Gbps信号之间的串扰,增大高速信号的抖动。由于该应用无法满足芯片原厂对系统链路的设计规则要求,鲜有厂商敢于尝试这项挑战芯片厂商设计规则的研发任务。但为了服务用户、满足客户边缘端极致化的AI算力需求,浪潮承接了这项高难度的研发任务。

规范要向应用妥协

要在1U的空间实现4颗AI芯片之间25Gbps跨板连接,就要解决信号跨板互连时的信号完整性问题。而造成信号失真的主要因素包括单板材料、传输长度、连接器性能及数量等等。

芯片厂商对芯片板卡上的信号损耗、回损、串扰都会有明确的要求:

芯片系统的链路总插损要小于21dB,其中芯片模组本身会占据8dB,留给系统的损耗为13dB。

最好的PCB板材,信号布线最长仍不能超过11英寸;

线路信号初始是900mV,到达接收端眼高会降低至0mV,需要靠芯片内部的补偿机制回复眼图。传输过程多使用连接器传输距离就要变短,同时链路串扰要增加。每多使用1个连接器,就需要把总线长缩短0.5英寸。同时链路串扰要小于7mV,多使用一次连接器,串扰会增加2mV左右。因此一般最多支持2个连接器。

“举例来说,信号在PCB线路中传输就像冰壶在冰面上滑行,滑行的最长距离取决于冰面本身的光滑程度,如果冰壶在冰面遇到障碍发生颠簸,或者和其他冰壶发生碰撞,就会减小冰壶滑行的最大距离。高速信号经过信道中的连接器,就像冰壶遇到冰面的障碍,会引起信号的抖动和衰减,可能会导致信号无法正确的传输到接收端。”浪潮研发工程师侯绍铮解释。

“但由于边缘端空间受限,4个AI模块无法放置于同一块单板上,要跨板连接就不得不在链路中增加连接器,那么如何系统性的减少链路长度、改善链路反射点性能、优化信号间的串扰是架构设计、信号完整性设计能力的重要指标,也是产品成功与否的关键能力。”

通过前期的仿真分析,浪潮选定背扣式,即方案二作为了设计方案。为了保持信号传输路径最短,满足插损要求,信号线的布线路径不能如下图左侧黄线路径设计,必须从连接器内部穿过。而这会导致25Gbps信号穿过25Gbps信号过孔(红圈)之间发生串扰。浪潮工程师通过合理的布线层设计及创新性使用背钻技术,改变过孔的长度,规避了线到孔的信号串扰。

高速信号过孔情况

依据芯片厂家的设计规则,要求AI模组端连接器有效过孔深度小于50mil,而跨板互连连接器又必须满足stub小于10mil的要求,两者在本方案中是冲突的。为了解决这一问题浪潮通过对有效孔长及stub对信号完整性的影响逐一仿真分析,并根据项目具体链路情况建模,先后仿真分析了3种不同布线方案的24种布线方式,依据该项目仿真结果同厂家规范允许的链路设计进行了对比,确定最终设计方案。

浪潮PCBA板布线方案

尽管项目的设计、器件选型、验证无论是难度还是复杂度都很高,但随着设计方案逐渐明晰,设计中的技术风险被一一攻克,浪潮开发的背扣式AI模组跨板互连方案,成功实现4个AI模组多次跨连接器的25Gbps互连,不仅达成了客户的规格需求,也完善了面向边缘端AI应用场景的服务器设计规范。

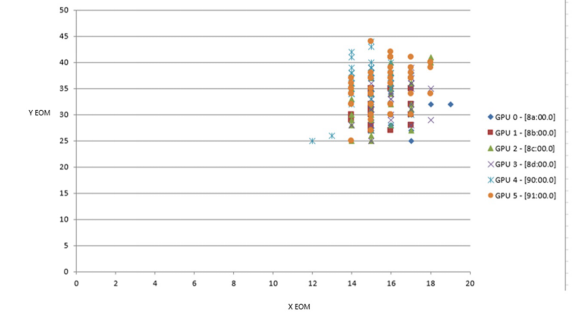

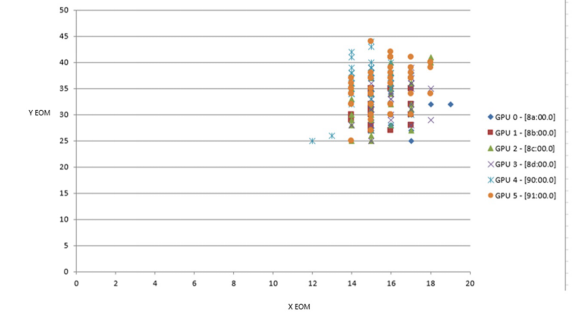

眼图结果

从AI到边缘,客户应用打破规范是未来的趋势

2019年5G商用牌照正式下发,5G刚刚开始,边缘计算也刚刚开始。靠近网络边缘侧的计算是场景化的,是高度应用驱动的,不论是一般性的计算还是边缘AI,都需要在实际应用中一步步探索。这个过程就是技术上创新的过程。

这种技术创新不单单是要满足更强的计算性能,更低的时延,更宽的带宽,更是一个以实际需求,客户实际应用驱动的不同技术标准和规范碰撞和调整的过程。可以预见,随着5G和AI等技术的发展,面对客户不同的边缘AI场景下海量的计算需求,将会有越来越多的厂商去打破行业规范,为边缘数据中心提供更加多元和创新的解决方案。

(免责声明:本网站内容主要来自原创、合作伙伴供稿和第三方自媒体作者投稿,凡在本网站出现的信息,均仅供参考。本网站将尽力确保所提供信息的准确性及可靠性,但不保证有关资料的准确性及可靠性,读者在使用前请进一步核实,并对任何自主决定的行为负责。本网站对有关资料所引致的错误、不确或遗漏,概不负任何法律责任。

任何单位或个人认为本网站中的网页或链接内容可能涉嫌侵犯其知识产权或存在不实内容时,应及时向本网站提出书面权利通知或不实情况说明,并提供身份证明、权属证明及详细侵权或不实情况证明。本网站在收到上述法律文件后,将会依法尽快联系相关文章源头核实,沟通删除相关内容或断开相关链接。 )